第二章阐述了对基于S5pv210处理器,UDA1341音频解码芯片,IIS串行数字音频总线的音频硬件体系架构的理解。

第三章阐述了音频硬件体系架构相对应的驱动架构和源码进行分析。

第四章基于Linux操作系统环境的简单音频处理系统。

第二章 硬件体系架构的分析

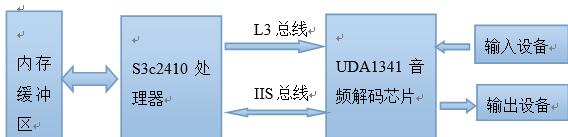

本章主要是对音频处理系统的硬件架构及各个部件的分析,这是一个基于S5pv210处理器,UDA1341音频解码芯片,IIS串行数字音频总线的体系架构。UDA1341芯片对音频信号进行编码和解码,也就是对数字信号和模拟信号信号进行相互转换,最后实现声音的录制及播放的功能,IIS总线则实现对音频数据的传输。系统的总体框架图如下:

图2-1 硬件架构框图

2.1 S5pv210处理器

2.1.1 S5pv210处理器结构概述

ARM硬件平台经过一系列版本的发展,性能比较稳定、完善,并具有开放性和可扩性。它能提供一些独特的性能来应对不同领域的需求,ARM处理器耗电少功能强、拥有16位/ 32位双指令集,寻址方式便捷,执行速度快,多处理器状态模式,便于系统的开发。本课题使用的是S5pv210处理器,该处理器应用非常广泛,为手机和一般的应用提供了高性能微处理器的解决方案。它采用了ARM Cortex TM-A8内核,实现了支持外围设备的V7指令集ARM体系结构。S5PV210处理器使用了许多外围硬件设备,使统总成本降低系而提高了整体功能,同时运用了许多低功率的技术使电池的使用寿命得到延长。它集成了很多所需要的组件,包含很多强大的硬件编解码功能,能够支持模拟/数字TV输出,实时视频和HDMI NTSC,PAL模式。

2.1.2 S5pv210处理器的特性

ARM Cortex TM-A8以附带NEON技术的CPU子系统为基础

64位的多层总线架构

工作频率可达到200 MHz,166 MHz,133 MHz

为移动应用提供了先进的电源管理

多格式编码,支MIPI-DSI和MIPI-CSI接口

一个AC-97音频编解码器接口和三通道的PCM系列音频接口

支持三个24位I2S接口和三个24位I2C接口

一个支持数字音频的TX S / PDI接口

系统定时器在电源中断模式下支持精确的时间记录(睡眠模式除外)

2.1.3 S5pv210处理器的结构框图

图2.1-1 S5pv210处理器框图

2.2 UDA1341音频解码芯片

2.2.1 UDA1341简介

UDA1341是一个支持立体声的芯片,它的信号处理机制使用了比特流转换技术,通过数字模拟转换器(DAC)和模拟数字转换器(ADC)对立体音频信号进行编码和解码。它很好地集成了前端的模拟,包括了自动增益控制(AGC)、可编程增益放大器(PGA)、数字信号处理器(DSP),可用PGA、AGC对模拟信号进行处理,对于数字信号,使用DSP功能,使设备能为基本的家庭立体声小型磁盘应用程序提供了极好的选择。同时由于其拥有低功耗和低电压的优势,也非常适用于便携式的应用程序。

2.2.2 UDA1341的L3总线和IIS总线接口

UDA1341芯片提供一组音频信号输出线和两组音频输入信号线与L3总线接口和IIS总线接口相对应。UDA1341芯片支持IIS总线的数据格式,包含IIS总线格式、右对齐串行格式和左对齐串行格式,同时提供了L3接口支持L3总线,便于微型控制器对于其微型控制器输入模式的控制。在微型控制器输入模式下,所有的数字声音处理功能和系统控制功能由微型控制器控制。

L3接口是一种常用的串行接口,经常用于UDA1341音频解码芯片和微型控制器之间的连接,进行数据信息和控制信息之间的交换。UDA1341音频解码芯片为此提供了一个串行硬件L3接口,由三个引脚组成: 嵌入式系统环境下的音频处理系统设计(3):http://www.751com.cn/jisuanji/lunwen_17153.html