4.4.3 地址模块 19

4.4.4 图像的显示 20

结 论 22

致 谢 23

参考文献24

1 绪论

1.1 LVDS技术的研究意义及发展现状

1.2 本文的研究背景

由于具有精度高、隐蔽性好和抗干扰能力强等一系列优点,红外成像制导技术一直是各国军方重点的研究方向之一。新一代红外制导技术更是对系统灵敏度和精确性提出了更高要求,这就要求红外视频图像传输具有更高的实时性以及抗噪性能,然而传统的数据传输方式如TTL、CMOS并行信号在传输速率、功耗、实时性以及噪声等方面存在的种种不足已经不能满足高速视频数据传输的需求。本课题就是在项目组的研究基础之上,对红外成像制导中红外视频的高速串行传输作前期准备。

1.3 本文的主要工作

本课题要求利用LVDS数据通信技术完成基于FPGA平台以及Quartus II软件的数字图像数据高速与低功耗传输,并实现接收数据的电视PAL制式显示。根据上述要求,通过查阅中外文献以及实践为基础,本文为LVDS图像传输做了如下工作:

(1)研究学习了LVDS接口通信技术原理,掌握了PAL制显示原理,以及Quartus II软件的使用,为系统设计提供了技术基础。

(2)掌握LVDS信号传输的硬件工作平台,确定图像传输与显示的总体方案,使用美国国家半导体公司的DS92LVl023E型串化器作为LVDS驱动端,DS92LVl224型解串器作为LVDS接收端。阅读其手册,掌握芯片组原理与使用。

(3)在Quartus II软件环境下进行FPGA数字电路设计,使用Verilog硬件描述语言编写程序分别驱动LVDS数字图像的发送端与接收端,并设计出满足传输技术要求的电路原理图,实现数字图像数据的高速串行传输。同时根据电视PAL制式的要求,通过FPGA平台对接收数据按照PAL制协议编程,然后送入显示器使图像正确显示。

2 LVDS概述

2.1 工作原理

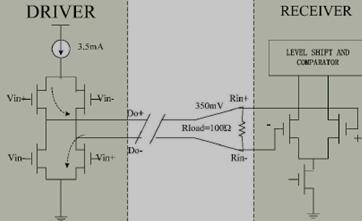

图 2.1 LVDS传输系统工作原理图

图2.1所示原理图:LVDS 驱动器主要包括3.5mA恒流源和电子开关,由于LVDS接收器具有高输入阻抗,驱动器输出的电流基本上全部流经100 Ω的匹配电阻Rload,并且由此在接收端上产生350mV的电压。当驱动器的数字差分输入信号翻转时,导致其驱动的电子开关翻转,它进而改变流经匹配电阻上的电流方向,从而通过差分变化产生有效的逻辑“1”(+350mv)和“0”(-350mv)状态。如图Vin+为高电平时,Vin-为低电平,虚线箭头表示电流流经方向,此时 LVDS 信号驱动输出数字逻辑“1”;当 Vin+为低电平且Vin-为高电平时,电流流经传输线的方向发生反转,此时输出的是数字逻辑“0”,在这两种状态下逻辑电平的摆幅都为350mV。接收端正确地接收到差分信号后,通过一系列电平转化和多级模拟比较器,最终输出全摆幅的数字信号,然后经过一定的缓冲驱动输出给数字系统。 基于FPGA的LVDS数字图像传输与显示(2):http://www.751com.cn/tongxin/lunwen_29300.html