通常量化有以下两种方法:一是“只舍不入”,二是“有舍有入”。前者舍去信号幅值小于量化单位Δ的部分,后者舍去信号幅值中小于量化单位Δ/2的部分,大于或等于Δ/2的部分计入。

A/D转换的最后阶段是编码。编码是指将量化信号的电平用数字代码来表示,编码方式有格雷码、自然二进制码和折叠二进制码等

2.1.3 主要性能指标

数据采集系统的性能指标主要取决于具体的任务要求及应用环境,以下介绍一些常用的指标。

(1)系统分辨率:等于一个量化单位,为A/D的位数直接相关。

(2)系统精度:指当系统工作在额定采样速率时,整个数据采集系统所能达到的转换精度。此外,系统精度和系统分辨率是不同的概念,精度是包含了分辨率、零位误差、零漂等各种误差因素。

(3)采集速率:是数据采集系统的重要参数,表示的是单通道采样能使用的最高采样频率,依据奈奎斯特采样定理,采样速率限制了采集系统能处理信号的最高频率。

2.2 数据采集系统的典型结构

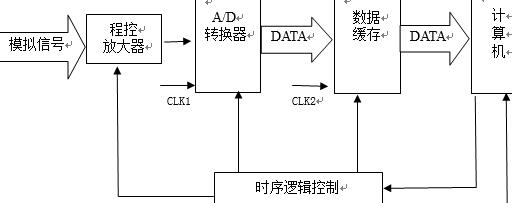

微电子技术和可编程逻辑器件的发展和普及使得数据采集系统得到了长足的发展,越来越多的领域选择使用数字处理系统完成任务。现代数据采集系统一般由计算机或大规模逻辑电路控制,A/D转换器将模拟信号转换成数字信号,为了匹配AD芯片的电压范围,模拟信号输入A/D转换器前要经过放大器放大,转换后的数字量存储在缓存器中,等待后续处理。数据采集系统一般由五个基本模块组成,结构框图如图2.1所示。

图2.1 数据采集系统框图

首先是程控放大器,传感器采集数据时,输出的模拟信号幅值较低,为了匹配A/D转换器的电压范围,一般都需要加前置放大器。被测信号在不同的场合表现不同的动态范围,单一的增益放大不能实现模数转换器与被测信号的匹配,因此使用程控放大器。

其次是A/D转换电路,它是采样通道的核心,模拟信号只有通过A/D采样电路才能转换成计算机能够识别的数字量。A/D电路的性能直接决定了数字采集系统的速率和精度,因此在设计中应着重考虑,依据任务要求选取合适的A/D芯片。

再次是数据缓存电路,A/D转换器将采样后得到的数字信号暂时存放在缓存电路中,同时,后续处理设备通过相应接口电路读取缓存电路中的数据进行处理。

然后是时序逻辑控制电路,系统的各个部分之间必须依照严格的定时关系协同工作,否则会造成严重的问题。定时电路依据系统的工作流程产生各种时序信号,逻辑控制电路则提供相应的控制信号,各个器件在时序和控制信号作用下工作。

最后是接口电路,它对信号进行整形或调整电平,然后传输给后续处理设备。

2.3 总体设计思路

本设计要求基于FPGA,设计完成高速实时数据采集、缓存与处理系统,系统具有大吞吐数据能力,具有良好的实时性和比较高的精度,由数据采集系统的任务可知,数据采集系统需要具备以下几个模块:程控放大器,ADC模块、FIFO和FFT模块。

传感器输出的模拟信号传输给A/D转换器,,ADC芯片在时钟信号的控制下完成模数转换,转换后的数字量存储在FIFO中。为了提高数据存储速度,本设计中采用乒乓式FIFO,FFT模块读取FIFO中数据进行预处理后传输给后续处理设备。整个过程中,FPGA产生各部分的控制信号,实现对整个系统的逻辑控制 FPGA高速数据采集与处理系统设计+源程序(3):http://www.751com.cn/zidonghua/lunwen_13844.html