1.2 VHDL与FPGA

VHDL语言是一种用于电路设计的高级语言。它在80年代的后期出现。最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言 。

VHDL翻译成中文就是超高速集成电路硬件描述语言,主要是应用在数字电路的设计中。目前,它在中国的应用多数是用在FPGA/CPLD/EPLD的设计中。当然在一些实力较为雄厚的单位,它也被用来设计ASIC。论文网

VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式、描述风格以及语法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

以硬件描述语言(Verilog或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC设计验证的技术主流。这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,但是功耗较低。但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。厂商也可能会提供便宜的但是编辑能力差的FPGA。因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。

1.3 基于FPGA的高精度小数分频器

对于小数分频的FGPA设计,目前广泛采用的方法是双模前置小数分频。双模前置小数分频器在理论上可以实现任意小数分频,但在实际的电路设计中,不可能真正实现任意小数分频,小数分频器的精度受控制计数器的影响,而控制计数器的设计会受硬件资源的限制(尽管FPGA有相当丰富的硬件资源)。

本课题的主要任务是:

(1).在QUARTUS-Ⅱ软件中用VHDL语言编写实现任意输入的分频系数的小数分频的程序。

(2).编写能够测定频率范围为0——99999999HZ的信号频率的VHDL程序。

(3).编写数码管动态显示的VHDL程序,便于测定小数分频器的输出信号频率。

(4).利用EDA实验箱仿真所编写的程序,并对仿真结果进行分析。

2 选择方案

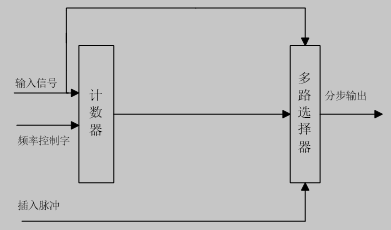

小数分频器的实现方法很多,但其基本原理都一样,即在若干个分频周期中采取某种方法使某几个周期少计一个或几个数,即吞脉冲原理,从而在整个计数周期的总体平均意义上获得一个小数分频比。

2.1积分分频器

积分分频器是比较常见的小数分频器,其基本原理是将小数分频比转换为整数值,再采用计数器对输入时钟进行计数,根据计数值吞掉一些脉冲,从而得到所需频率的输出:

基于FPGA的高精度小数分频器的设计+程序(2):http://www.751com.cn/zidonghua/lunwen_71528.html

基于FPGA的高精度小数分频器的设计+程序(2):http://www.751com.cn/zidonghua/lunwen_71528.html