通过分析目前数字滤波器的几种实现方法,本文认为基于FPGA的数字滤波器具有许多优势,本文考虑到信息技术的发展对于数字滤波器的标准越来越高,而目前FIR数字滤波器的性能还不健全,于是选择了基于FPGA的数字滤波器作为主要研究内容,卷积运算经常运用于滤波器的数据处理中,在设计中解决这些乘法运算的方法是将它们转换成加减法,这是目前解决乘法运算的主要思想。设计前期在Matlab中对滤波器原理进行证明包括(零极点图、时域和频域图等),分析FIR数字滤波器的多种设计思想和窗函数选择方法,在设计后期对FIR数字滤波器的小数乘法问题进行单独验证。然后对分析出来的问题进行论证和解决,最后在QUARTUSⅡ中进行仿真实现。

数字滤波器(Digital filter)是由加法器、数字乘法器和延时单元组成的一种器件。它的功能是对输入离散信号的数字代码进行运算处理,从而达到改变信号频谱的目标。可认为是一个离散时间系统按预定的算法,将输入离散时间信号转换为所要求的输出离散时间信号的特定功能装置FIR(Finite Impulse Response )。由线性系统理论可知,在某种合适条件下,输入到线性系统的一个冲击完全可以反应出系统。当我们处理有限的离散数据时,线形系统的响应也是有限的。若线性系统是一个空间滤波器,则通过简要地观察它对冲击的响应,我们就可以完全计算出该滤波器。由这种方式确定的滤波器称之为有限冲击响应(FIR)滤波器。

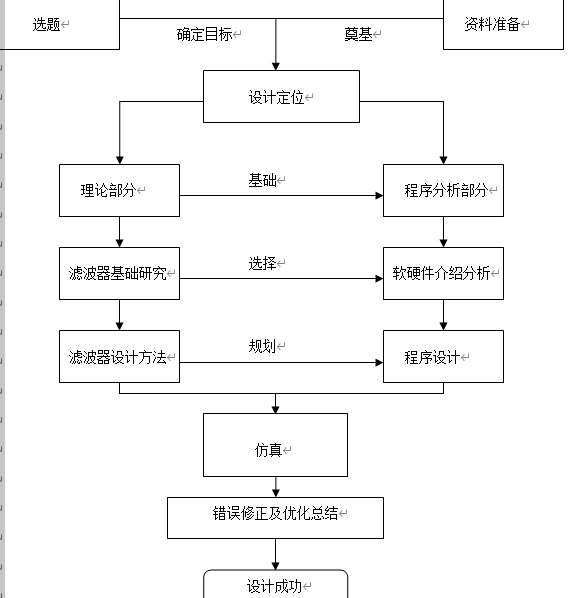

图1-1总体设计过程图

2 FIR数字滤波器的参数设计

2.1 FIR滤波器的功能

数字滤波器的功能通常是用来变换时域或者频域中一些要求信号的属性,过滤信号中某一部分频率分量。经过数字滤波器的信号是让其频谱与数字滤波器的频率响应相乘而后得出新的结果。通过一个线性卷积过程,从时域上输入信号与滤波器的单位冲击响应作卷积和。

FPGA的FIR滤波器设计(2):http://www.751com.cn/zidonghua/lunwen_73616.html