1.1 数字鉴相器的研究背景论文网

1.1.1 I/Q 双通道处理

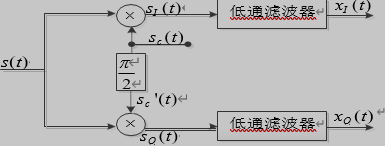

图 1.1 正交相位检波器框图

上0中,中频回波信号表示为 s(t) ,本地振荡信号表示为 sc (t) ,其中:

经过正交混频和低通滤波器处理后得输出的正交双通道信号为:

1.2 DSP 系统概述

1.2.1 DSP 系统的信号处理方式

DSP 是指利用专用处理设备,以数字形式对信号进行的采集、变换、滤波、估值、 增强、压缩、识别等处理、DSP 系统要处理的信号多为自然信号,因此首先需要通过 传感器将自然信号转换为电信号。其次要对自然界的信号进行数字处理,就必须通

过 A/D 模块将其转换为数字形式。继而 DSP 对数字信号进行抽样,并非输入的的数 字信号进行某种处理,如一系列的乘累加操作、对数据进行分析、提取、还原,对 数据进行快速存储或传输等。DSP 芯片完成数字处理后,有时还必须要通过 D/A 模块 把处理后的数字信号重新还原为模拟信号。这是整个系统的核心,如图 1.2 所示:

图 1.2 DSP 系统的信号处理方式

1.2.2 基于 DSP 的信号处理系统功能框图

一般的,输入信号首先进行带限滤波和抽样,然后进行模/数(A/D)变换将信号 变换为数字比特流。根据奈奎斯特抽样定理,对低通模拟信号,为保持信息的不丢 失,抽样频率至少必须是输入带限信号最高频率的 2 倍。DSP 芯片的输入是时间离散 的数字信号,根据系统要求,DSP 芯片对输入信号按照 A/D 变换后得到定的算法进行 处理,这是 DSP 系统的关键。最后处理后的数字样值再经数/模(D/A)变换转换为 模拟样值,之后再进行平滑滤波的)就可以得到连续的模拟波形。图 1.3 是基于 DSP 的信号处理系统功能框图[10]。

图 1.3 基于 DSP 的信号处理系统功能框图

DSP 芯片是一种特别适合于进行数字信号处理运算的微处理器,其主要应用是 实时快速地实现各种数字信号处理算法,一般具有如下主要特点:

(1)在一个指令周期内可完成一次乘法和加法;(2)程序和数据空间分开, 可以同时访问指令和数据;(3)片内具有快速 RAM,通常可通过独立的数据总线在 两块中同时访问; (4)具有低开销或无开销循环及跳转的硬件支持;(5)快速 的中断处理和硬件 I/O 支持;(6)具有在单周期内操作的多个硬件地址产生

器; (7)可以并行执行多个操作;(8)支持流水线操作,使取指、译码和执行 等操作可以重叠执行。

下图是 DSP 应用系统的一般流程如图 1.4 所示:

图 1.4 DSP 应用系统的一般流程图

1.2.4 DSP 芯片 TMS320F2812 的性能特点

TMS320F2812 是 TI 公司专门用于控制的一款高性能、多功能、高性价比的定点 32 位 DSP 处理芯片。该芯片最高可以以 150MHz 主频工作,并带有 18K×16 位零等待 周期的片内 SRAM 和 128K×16 位片内 Flash(存取时间为 36ns)。该器件还有 3 个 独立的 32 位 CPU 定时器,以及 56 个可独立编程的 GPIO 引脚,还可外扩大于 1M×16 位程序和数据存储器。该芯片片上外设主要包括 16 路 12 位精度的 ADC(最快 80ns 转换时间)、2 路 SCI(SCIA 和 SCIB)、1 路 SPI、1 路 McBSP、1 路 eCAN,以及两 个事件管理模块(EVA 和 EVB)等。每个事件管理模块包括 6 路 PWM/CMP、2 路 QEP、 3 路 CAP 和 2 路 16 位的定时器。 DSP单脉冲雷达鉴相器的硬件电路设计+PCB电路图(2):http://www.751com.cn/zidonghua/lunwen_76961.html