- 上一篇:基于ARM和GPRS的无线数据传输系统设计

- 下一篇:FPGA的MQAM调制器的分析与实现+程序

此次设计采用将元件值归一化法,将低通原型滤波器的阻抗和频率作归一化处理,使得滤波器设计通用化,设计一个符合标准要求的低通滤波器。低通滤波器指标为:通带截止频率为fp=120MHz;通带内最大衰减为Amax=0.2dB;在fs=135 MHz处阻带内最小衰减为Amin=66dB。

选择multisim 10.0作为仿真软件,掌握使用方法,通过对电路的连接仿真分析,巩固所学的理论知识,做到学以致用。对设计的低通滤波器电路结构进行仿真分析,并验证所得到的结果。

2 直接数字频率合成器DDS

2.1 DDS的组成

直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

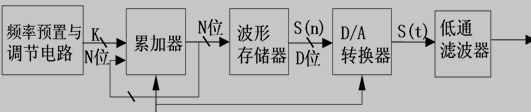

DDS的基本结构如下图2.1所示:

图2.1 DDS的结构图

DDS主要由频率预置与调节电路、累加器、波形存储器、D/A转换器、低通滤波器构成,频率预置与调节电路是实现频率控制量的输入,不变量K被称为相位增量,也叫频率控制字。频率控制字的值可以由EDA实验系统提供的若干个开关直接输入,也可以由一个外部开关控制计数器产生相应的频率控制字。

累加器原理如图2.2所示:

累加器原理图

它由N位加法器N位寄存器构成。每来一个时钟,加法器就将频率控制字K与累加相位数据相加,相加的结果有反馈送至寄存器的数据输出端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位相加器在每一个时脉冲输入时,把频率控制字累加一次,相位累加器的溢出频率就是DDS输出的信号频率。由于相位累加器为N位,相当于把正弦信号在相位上的精度定为N位,所以分辨率为1/ ,若系统基准时钟频率 源:自~751-·论`文'网·www.751com.cn/

为 ,频率控制字K为1,则DDS输出最小频率为 = / ;DDS输出的最高频率由 Nyquist采样定理决定,即 /2(K的最大值为2N-1);若K为B,则输出频率为: =B× / 。

用相位累加器输出的数据作为波形存储器(ROM)相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。N位的寻址ROM相当于把 ~ 的正弦信号离散成具有 个样值的序列,若波形ROM有D位数据位,则 个样值的幅值以D位二进制数值固化在ROM中,按照地址的不同可以输出相应的正弦信号的幅值。选取ROM的地址(即相位累加器的输出数据)时,可以间隔选项,相位寄存器输出的位数N一般取10-16位,这种载取方法称为截断式用法,以减少ROM的容量。N太大导致ROM容量的成倍上升,而输出精度受D/A位数的限制未有很大改善。

D/A转换器的作用:把已经合成的正弦波的数字量转换成模拟量。正弦幅度量化序列经D/A转换后变换成了包络为正弦波的阶梯波。波形存储器的输出送到D/A转换器,由D/A转换器将数字信号转换成模拟信号输出。

DDS具有相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面的优点。但是它的缺点就是输出频率越接近Nyquist带宽的高端,采样点数越少,其输出的杂散干扰就越大,DDS 芯片的输出具有大量的谐波分量和系统时钟干扰。文献综述

2.2 DDS的应用

由于DDS的特点以及一些公司不断推出DDS芯片和产品。DDS技术被广泛用于雷达、通信、电子对抗和仪器仪表等领域。