- 上一篇:道路交通事故分级报警及二次事故预警系统设计

- 下一篇:水下纯方位系统目标跟踪算法研究

1.4 边界扫描结构和IEEE1149_1标准:

由于 EDA 技术的广泛应用,微电子技术的迅猛发展,组装工艺的不断更新,使得通讯电子产品,芯片、单板、系统的复杂度不断提高,物理尺寸却在不断缩小。随之而来的就是测试问题的复杂化,测试的成本,周期都在急剧增加。针对这种情况,电子测试的研究方向随之发展到了研究在电子系统甚至芯片设计时就考虑系统测试问题的新兴设计方法——DFT[5]。而边界扫描就是一种重要的有效的测试方法,它的广泛应用对降低测试难度,提供测试质量,提高产品故障定位能力等各方面都有重大意义。

边界扫描机制的主要思想是:通过在芯片管脚和芯片内部逻辑电路之间,即在靠近芯片的输入输出管脚上增加一个移位寄存器单元。因为这些移位寄存器单元都分布在芯片的边界上(周围),所以被称为边界扫描寄存器[6]。边界扫描测试(BST)技术目前主要应用于电子系统的板级测试。[7]

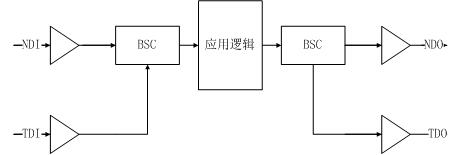

图1给出了一个带应用逻辑和相关的输入输出和由串行边检扫描单元(BSC)组成的边界扫描通道的IC示意图,该图中每个IC功能管脚有一个BSC。[8]

图1.1 边界扫描示例

边界扫描与器件的功能和复杂度无关,测试端口也与器件的物理尺寸无关,只需少量的寄存器即可完成器件或系统的自动测试和编程。[9]互联的BSC在主IC测试数据输入(TDI)管脚和测试数据输出(TDO)管脚之间组成了一个扫描通道,在正常的IC操作中,输入和输出信号可以从正常的数据输入(NDI)到正常的数据输出(NDO),自由地通过每个BSC。[4]然而,当进入边界扫描模式时,测试激励可以从每一个BSC的输出端进入,测试响应可以在每个BSC的输出端捕获并移出,以便于观察。集成线路板上线路互联和相邻IC的外部测试通过在输出BSC施加测试激励,并在输入BSC处捕捉测试响应来完成。作为一种选择,应用逻辑的内部测试可以通过在输入BSC施加测试激励,并在输出BSC捕获测试响应来完成。在IC的设计中,边界处扫描通道的应用提供了嵌入式测试能力,这种测试能力克服了目前和将来的板级设计中的物理访问入口问题。[10]

IEEE 1149.1标准规定的边界扫描结构由指令寄存器、旁路寄存器、边界扫描寄存器、可选的用户数据寄存器、测试读取端口(TAP)组成,指令寄存器和数据寄存器是在主要的测试数据输入(TDI)管脚和输出管脚之间独立的扫描通道,该结构允许TAP在不进入其他扫描通道的情况下,通过指令或数据两种扫描通道选择和移动数据。[11]

指令寄存器提供在扫描通道中访问特定的数据寄存器所需要的地址和控制信号,当TAP接到一个指令寄存器扫描指令时,访问指令寄存器。在指令寄存器扫描操作过程中,来自TAP的SELECT输出选择指令寄存器的输出驱动TDO管脚。图2给出了一种通用指令寄存器的结构。

-

MSP430单片机多功能电能表设计+电路图

-

MSP430开发板扩展板设计+程序

-

MSP430无线传感器网络的家...

-

MSP430物联网的智能农业数...

-

MSP430单片机自动搬运控制...

-

LabVIEW+MSP430便捷式机械设备...

-

MSP430单片机的汽车动载测...

河岸冲刷和泥沙淤积的监测国内外研究现状

电站锅炉暖风器设计任务书

java+mysql车辆管理系统的设计+源代码

乳业同业并购式全产业链...

当代大学生慈善意识研究+文献综述

中考体育项目与体育教学合理结合的研究

酸性水汽提装置总汽提塔设计+CAD图纸

大众媒体对公共政策制定的影响

十二层带中心支撑钢结构...

杂拟谷盗体内共生菌沃尔...